Jacob, A. P. et al. Scaling challenges for advanced CMOS devices. Int. J. High Speed Electron. Syst. 26, 1740001 (2017).

Google Scholar

Akinwande, D. et al. Graphene and two-dimensional materials for silicon technology. Nature 573, 507–518 (2019).

Google Scholar

Chhowalla, M., Jena, D. & Zhang, H. Two-dimensional semiconductors for transistors. Nat. Rev. Mater. 1, 16052 (2016).

Google Scholar

Zeng, S., Liu, C. & Zhou, P. Transistor engineering based on 2D materials in the post-silicon era. Nat. Rev. Electr. Eng. 1, 335–348 (2024).

Das, S., Chen, A. & Marinella, M. Beyond CMOS. In Proc. 2021 IEEE International Roadmap for Devices and Systems Outbriefs 1–129 (IEEE, 2021).

Chubarov, M. et al. Wafer-scale epitaxial growth of unidirectional WS2 monolayers on sapphire. ACS Nano 15, 2532–2541 (2021).

Google Scholar

Li, T. et al. Epitaxial growth of wafer-scale molybdenum disulfide semiconductor single crystals on sapphire. Nat. Nanotechnol. 16, 1201–1207 (2021).

Google Scholar

Wang, J. et al. Dual-coupling-guided epitaxial growth of wafer-scale single-crystal WS2 monolayer on vicinal a-plane sapphire. Nat. Nanotechnol. 17, 33–38 (2022).

Google Scholar

Shen, P.-C. et al. Ultralow contact resistance between semimetal and monolayer semiconductors. Nature 593, 211–217 (2021).

Google Scholar

Li, W. et al. Approaching the quantum limit in two-dimensional semiconductor contacts. Nature 613, 274–279 (2023).

Google Scholar

McClellan, C. J., Yalon, E., Smithe, K. K., Suryavanshi, S. V. & Pop, E. High current density in monolayer MoS2 doped by AlOx. ACS Nano 15, 1587–1596 (2021).

Google Scholar

Arutchelvan, G. et al. Impact of device scaling on the electrical properties of MoS2 field-effect transistors. Sci. Rep. 11, 6610 (2021).

Google Scholar

Dorow, C. et al. Advancing monolayer 2-D nMOS and pMOS transistor integration from growth to Van Der Waals interface engineering for ultimate CMOS scaling. IEEE Trans. Electron Devices 68, 6592–6598 (2021).

Google Scholar

Chou, A.-S. et al. Antimony semimetal contact with enhanced thermal stability for high performance 2D electronics. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 7.2.1–7.2.4 (IEEE, 2021).

O’Brien, K. P. et al. Advancing 2D monolayer CMOS through contact, channel and interface engineering. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 7.1.1–7.1.4 (IEEE, 2021).

Chou, A. S. et al. High-performance monolayer WSe2 p/n FETs via antimony-platinum modulated contact technology towards 2D CMOS electronics. In Proc. 2022 International Electron Devices Meeting (IEDM) 7.2.1–7.2.4 (IEEE, 2022).

Pang, C.-S. et al. Atomically controlled tunable doping in high-performance WSe2 devices. Adv. Electron. Mater. 6, 1901304 (2020).

Google Scholar

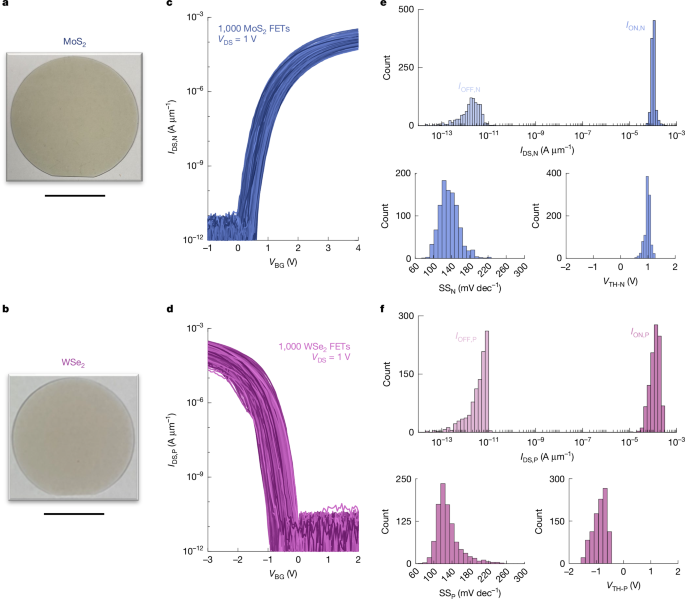

Dorow, C. J. et al. Exploring manufacturability of novel 2D channel materials: 300 mm wafer-scale 2D NMOS & PMOS using MoS2, WS2, & WSe2. In Proc. 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023).

Cai, L. et al. Rapid flame synthesis of atomically thin MoO3 down to monolayer thickness for effective hole doping of WSe2. Nano Lett. 17, 3854–3861 (2017).

Google Scholar

Chiang, C. C., Lan, H. Y., Pang, C. S., Appenzeller, J. & Chen, Z. Air-stable p-doping in record high-performance monolayer WSe2 devices. IEEE Electron Device Lett. 43, 319–322 (2022).

Google Scholar

Wachter, S., Polyushkin, D. K., Bethge, O. & Mueller, T. A microprocessor based on a two-dimensional semiconductor. Nat. Commun. 8, 14948 (2017).

Google Scholar

Polyushkin, D. K. et al. Analogue two-dimensional semiconductor electronics. Nat. Electron. 3, 486–491 (2020).

Google Scholar

Pang, C.-S., Thakuria, N., Gupta, S. K. & Chen, Z. First demonstration of WSe2 based CMOS-SRAM. In Proc. 2018 IEEE International Electron Devices Meeting (IEDM) 22.2.1–22.2.4 (IEEE, 2018).

Cao, W., Kang, J., Sarkar, D., Liu, W. & Banerjee, K. 2D semiconductor FETs—projections and design for sub-10 nm VLSI. IEEE Trans. Electron Devices 62, 3459–3469 (2015).

Google Scholar

Lu, Y.-C., Huang, J.-K., Chao, K.-Y., Li, L.-J. & Hu, V. P.-H. Projected performance of Si-and 2D-material-based SRAM circuits ranging from 16 nm to 1 nm technology nodes. Nat. Nanotechnol. 19, 1066–1072 (2024).

Sylvia, S. S., Alam, K. & Lake, R. K. Uniform benchmarking of low-voltage van der Waals FETs. IEEE J. Explor. Solid-State Comput. Devices Circuits 2, 28–35 (2016).

Google Scholar

Guan, S.-X. et al. Monolithic 3D integration of back-end compatible 2D material FET on Si FinFET. NPJ 2D Mater. Appl. 7, 9 (2023).

Jayachandran, D., Sakib, N. U. & Das, S. 3D integration of 2D electronics. Nat. Rev. Electr. Eng. 1, 300–316 (2024).

Agarwal, T. et al. Benchmarking of monolithic 3D integrated MX2 FETs with Si FinFETs. In Proc. 2017 IEEE International Electron Devices Meeting (IEDM) 5.7.1–5.7.4 (IEEE, 2017).

Jayachandran, D. et al. Three-dimensional integration of two-dimensional field-effect transistors. Nature 625, 276–281 (2024).

Google Scholar

Pendurthi, R. et al. Monolithic three-dimensional integration of complementary two-dimensional field-effect transistors. Nat. Nanotechnol. 19, 970–977 (2024).

Google Scholar

Ghosh, S. et al. Monolithic and heterogeneous three-dimensional integration of two-dimensional materials with high-density vias. Nat. Electron. 7, 892–903 (2024).

Google Scholar

Radisavljevic, B., Whitwick, M. B. & Kis, A. Integrated circuits and logic operations based on single-layer MoS2. ACS Nano 5, 9934–9938 (2011).

Google Scholar

Zhang, H. et al. Complementary logic with voltage zero-loss and nano-watt power via configurable MoS2/WSe2 gate. Adv. Funct. Mater. 28, 1805171 (2018).

Google Scholar

Guo, Y. et al. Van der Waals polarity-engineered 3D integration of 2D complementary logic. Nature 630, 346–352 (2024).

Google Scholar

Pendurthi, R. et al. Heterogeneous integration of atomically thin semiconductors for non-von Neumann CMOS. Small 18, 2202590 (2022).

Google Scholar

Du, W. et al. Low-power-consumption CMOS inverter array based on CVD-grown p-MoTe2 and n-MoS2. iScience 24, 103491 (2021).

Google Scholar

Zhu, H. et al. Step engineering for nucleation and domain orientation control in WSe2 epitaxy on c-plane sapphire. Nat. Nanotechnol. 18, 1295–1302 (2023).

Google Scholar

Li, Y., Hwang, C.-H. & Cheng, H.-W. Process-variation- and random-dopants-induced threshold voltage fluctuations in nanoscale planar MOSFET and bulk FinFET devices. Microelectron. Eng. 86, 277–282 (2009).

Google Scholar

Zhao, P. et al. Air stable p-doping of WSe2 by covalent functionalization. ACS Nano 8, 10808–10814 (2014).

Google Scholar

Clark, L. T. et al. ASAP7: A 7-nm finFET predictive process design kit. Microelectronics J. 53, 105–115 (2016).

Google Scholar

Huang, J.-K. et al. High-κ perovskite membranes as insulators for two-dimensional transistors. Nature 605, 262–267 (2022).

Google Scholar

Illarionov, Y. Y. et al. Ultrathin calcium fluoride insulators for two-dimensional field-effect transistors. Nat. Electron. 2, 8–13 (2019).

Google Scholar

Illarionov, Y. Y. et al. Insulators for 2D nanoelectronics: the gap to bridge. Nat. Commun. 11, 3385 (2020).

Google Scholar

Yang, A. J. et al. Van der Waals integration of high-κ perovskite oxides and two-dimensional semiconductors. Nat. Electron. 5, 233–240 (2022).

Google Scholar

Foster, C. C. Something new: the Intel MCS-4 micro computer set. ACM SIGARCH Comput. Archit. News 1, 16–17 (1972).

Mori, R., Tajima, H., Tajima, M. & Okada, Y. Microprocessors in Japan. Euromicro Newsl. 3, 50–57 (1977).

Google Scholar

Dingwall, A. G. F., Stricker, R. E. & Sinniger, J. O. A high speed bulk CMOS C/SUP 2/L microprocessor. IEEE J. Solid-State Circuits 12, 457–462 (1977).

Shulaker, M. M. et al. Carbon nanotube computer. Nature 501, 526–530 (2013).

Google Scholar

Hills, G. et al. Modern microprocessor built from complementary carbon nanotube transistors. Nature 572, 595–602 (2019).

Google Scholar

Xuan, Y. et al. Multi-scale modeling of gas-phase reactions in metal-organic chemical vapor deposition growth of WSe2. J. Cryst. Growth 527, 125247 (2019).

Google Scholar

Sebastian, A., Pendurthi, R., Choudhury, T. H., Redwing, J. M. & Das, S. Benchmarking monolayer MoS2 and WS2 field-effect transistors. Nat. Commun. 12, 693 (2021).

Google Scholar

Dodda, A. et al. Active pixel sensor matrix based on monolayer MoS2 phototransistor array. Nat. Mater. 21, 1379–1387 (2022).

Google Scholar

Ghosh, S. et al. An all 2D bio-inspired gustatory circuit for mimicking physiology and psychology of feeding behavior. Nat. Commun. 14, 6021 (2023).

Google Scholar

Cheng, Z. et al. Immunity to contact scaling in MoS2 transistors using in situ edge contacts. Nano Lett. 19, 5077–5085 (2019).

Google Scholar

Dorow, C. J. et al. Gate length scaling beyond Si: mono-layer 2D channel FETs robust to short channel effects. In Proc. 2022 International Electron Devices Meeting (IEDM) 7.5.1–7.5.4 (IEEE, 2022).

Kwon, J. et al. 200-mm-wafer-scale integration of polycrystalline molybdenum disulfide transistors. Nat. Electron. 7, 356–364 (2024).

Google Scholar

Chou, A.-S. et al. High on-current 2D nFET of 390 μA/μm at VDS = 1 V using monolayer CVD MoS2 without intentional doping. In Proc. 2020 IEEE Symposium on VLSI Technology 1–2 (IEEE, 2020).

Fang, H. et al. High-performance single layered WSe2 p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

Google Scholar

Dorow, C. J. et al. Advancing monolayer 2D NMOS and PMOS transistor integration from growth to van der Waals interface engineering for ultimate CMOS scaling. In Proc. 2021 Symposium on VLSI Technology 1–2 (IEEE, 2021).

Yang, S., Lee, G. & Kim, J. Selective p-doping of 2D WSe2 via UV/ozone treatments and its application in field-effect transistors. ACS Appl. Mater. Interfaces 13, 955–961 (2021).

Google Scholar

Pandey, S. K. et al. Controlled p-type substitutional doping in large-area monolayer WSe2 crystals grown by chemical vapor deposition. Nanoscale 10, 21374–21385 (2018).

Google Scholar

Vu, V. T. et al. One-step synthesis of NbSe2/Nb-doped-WSe2 metal/doped-semiconductor van der Waals heterostructures for doping controlled ohmic contact. ACS Nano 15, 13031–13040 (2021).

Lan, H.-Y., Tripathi, R., Liu, X., Appenzeller, J. & Chen, Z. Wafer-scale CVD monolayer WSe2 p-FETs with record-high 727 μA/μm Ion and 490 μS/μm gmax via hybrid charge transfer and molecular doping. In Proc. 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023).

Mortelmans, W. et al. Record performance in GAA 2D NMOS and PMOS using monolayer MoS2 and WSe2 with scaled contact and gate length. In Proc. 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2024).